NASA TT F-8591

CANDIDE: OVERALL PLAN FOR POSSIBLE DEVELOPMENTS OF

LINKAGE OF THE CETIS ANALOG AND DIGITAL COMPUTERS

A. Riotte Jan 1964

| وں،      | 'N71-714                      | 96          |

|----------|-------------------------------|-------------|

| FORM 6   | (PAGES)                       | NONE (CODE) |

| FACILITY | (NASA CR OR TMX OR AD NUMBER) | (CATEGORY)  |

Translation of "CANDIDE - Plan d'ensemble sur les dévelopements possibles du couplage des calculateurs analogiques et digitaux du CETIS"

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

WASHINGTON

January 1964

EUR 150.f

COMMUNAUTÉ EUROPÉENNE DE L'ÉNERGIE ATOMIQUE-EURATOM

CANDIDE: OVERALL PLAN FOR POSSIBLE DEVELOPMENTS OF LINKAGE OF THE CETIS ANALOG AND DIGITAL COMPUTERS

A. RIOTTE

1963

Centre Commun de Recherche Nucléaire Etablissement d'Ispra - Italie Centre Européen de Traitement des Informations Scientifiques-CETIS

CETIS Report No. 33, 1963

| Typed by             | Corrections | propired | ძ ხუ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Proofrend by         | Corrections | ` .      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Corrections typed by | final check | : by     | manus and a second seco |

## CONTENTS Page Introduction Present Position of the APACHE Code . . . . . . . . . 2. Review of Numerical Inputs and Outputs Available 2.1.3 Results in dynamic output ....... 5 3.1 Linkages in the digital-to-analog direction . . . . . . 6 6 3.2 Two-way linkage 9 9 Ancillary Studies 10 4.1 Automatic verification of analog function . . . . . . . 10 10 4.1.2 Static check processing . . . . . . . 12 4.2 Constitution of a library of subroutines in APACHE 2 . . 12 4.3 Special programs connected with problems to be solved . . 12 4.5 Application to the CARN project . . . . . . . . . . . . . . . . 13 13 15

| Typed by             | Corrections prochased by |

|----------------------|--------------------------|

| · · ·                | Conscions out in by      |

| Corrections typed by | Fine check by            |

#### SUMMARY

The studies required for development of linkages between the CETIS analog and digital computers are described. Two types of linkage are distinguished:

- l. One-directional static or structural linkage by which the analog computer is placed under the direct or indirect control of the digital computer for the set-up phase. The problem is furnished to the computer in the form of a digital program in APACHE code, and

- 2. Dynamic two-directional linkage. The digital computer after analog-digital conversion processes the analog values and restores others by digital-analog conversion, thus acting as a function generator.

A study plan to divide the theoretical and practical work into stages is presented, with time estimates.

Author

Since the association of teams specializing in the two types of computers at CETIS has already born fruit in the form of the APACHE code, the need arises for establishment of an overall plan for development of a direct analog-digital linkage.

For several years, the bringing together of the two disciplines has been attempted in various ways, either by considering the ordinator as a digital computer in real time, simulating the part of the problem processed digitally in reality (control of machinery, for example, Ref. 1), or by splitting up the problem into sequences of successive analog schemas, a digital memory connecting the preceding with that which follows (Ref. 5). Other methods have been investigated: one of them which is well known consists in organizing a digital computer as an analog computer with a view to parallel functioning of the circuits (Digital Differential Analyzer). Attempts have been made at digital programming before analog set-up (Refs. 4, 8). Finally, in the course of preliminary study from which the present report derives, there has been an opportunity to become acquainted with a project (Ref. 9) whose goals and approach parallel ours, but without sufficient detail to permit an exact comparison.

| Maria de la Companya |             |           |         |

|----------------------------------------------------------------------------------------------------------------|-------------|-----------|---------|

| Typed by                                                                                                       | Corrections | proofree  | d by    |

| Proofreed by                                                                                                   | Corrections | cut in by | <i></i> |

| Corrections typed by                                                                                           | Final sheck | cby _     |         |

The following study plan was established primarily to exploit with maximum effectiveness the analog complex existing at CETIS and to increase its potentialities and the reliability of its use by means of linkage with the powerful neighboring digital installation.

#### 1. Present Position of the APACHE Code

APACHE 1 is being used. It permits preparation of the setup and static check of a problem on an analog computer by means of IBM 1620 (Ref. 7). It must be regarded as a code for intra-CETIS use, permitting those who apply it to draw from it experience that is requisite for construction of the definitive APACHE 2 code. Indeed, although it functions adequately within initially fixed limits, it is to be wished that two different types of codes will not be started which refer to two stages of the same problem. Moreover APACHE 2 in the course of definition at the Computer Center will respond to requirements clearly more ambitious than those imposed upon APACHE 1. Intended to be used on IBM 7090, it will allow:

- 1. Direct processing of high order differential equations without breakdown into equations of the first order,

- 2. Writing with marked variables, and

- 3. Introduction of subroutines corresponding to library block diagrams.

The first condition will radically ease the writing of the program. It will also allow:

- 1. In addition to processing of data furnishing setup coefficients of the potentiometers and the static check (these already provided by APACHE 1), an automatic addressing of the elements of the analog computer: amplifiers, potentiometers, logical functions, nonlinearities.

- 2. An optimizing of the beta factor, representing the relationship of machine time to the independent variable of the problem, and

- 3. A preparation of stages of computation by partial modifications of the program.

Finally an adaptation of this definitive code for its use on IBM 1620 with punched card inputs and outputs, indirect addressing system and 40,000 memory positions is envisioned as of now, in order to permit a possible spread to analog computer centers. Indeed, these centers can contemplate acquisition of such a machine that would justify itself by the substantial increase of power, reliability and speed of the installation.

All that precedes constitutes the language permitting digital processing of information bits contained in the data. The result determines

| Typed by             | Corrections proofreed by |

|----------------------|--------------------------|

| Proofreed by         | Corrections cut in by    |

| Corrections typed by | Final check by           |

the choice of special structure that the analog computer assumes upon resolution of the problem. It is accessible to the user in form of a control register which picks up the data, associating to them all the requisite information (such as choice of scales, initial values, static check, distribution by address of the operation to the computers, etc.).

There remain to be specified the various existing and nonexistent organs that will support the practical embodiment of this structure, and to state precisely what stages can reasonably be provided before the achieving of a two-way dynamic linkage.

2. Review of Numerical Inputs and Outputs Available on the Two Types of Computers

The present computer material comprises analog and digital computers, of which the former have possibilities of numerical command for certain elements.

#### 2.1 Analog computer

The Analog Section installation comprises Electronic Associates 231 R with ADIOS console (Automatic Digital Input Output System). When a problem is put on the machine, the data inputs are of various types.

- 2.1.1 Setup or pre-computation data

- 2.1.1.1 Value of the numerical coefficients

The table of numerical coefficients corresponds to the furnishing of parameter data and initial conditions. It can be introduced by perforated tape (FRIDEW perforator and reader), the code used being a 7-channel code (Ref. 10).

2.1.1.2 Setup of the block diagram

It corresponds to topological connection between units of computation and it is achieved manually by introduction of pins in the hubs of the patch board. Since the coordinates of the points to be connected are assumed to be furnished by the program, the operation can be regarded as a purely manual one.

## 2.1.1.3 Setup of function generators

The constitution of present function generators (DFG, pot padders) provides only manual setup on the potentiometer of points determined by an analysis of the furnished curves: mathematical or experimental functions.

| Typed by             | Corrections | proofree  | d by |

|----------------------|-------------|-----------|------|

|                      | Corrections | cut in by | 1    |

| Corrections typed by | Final check | . by      |      |

The setup of functions of two or more variables can be carried by various procedures, depending upon the required precision, to a fragment of the block diagram that uses the existing units including function generators, within the range of the available material.

## 2.1.1.4 Register of various cases of computation

It can be characterized by modifications of parameters, of initial conditions, of block diagram, of setup of function generators. The first two cases occur with the introduction of a new perforated tape in the ADIOS console, while the last two necessitate a manual intervention.

## 2.1.2 Results in static output

When the 231 R's are stopped in the course of computation, either at the end of a predetermined period or by comparison of a variable with a preset value, the ADIOS console allows numerical readout, printed by a typewriter, of values taken by all the variables in play at the moment of halting, and their transfer on perforated tape according to a reading program that states the units of which the output value is desired.

## 2.1.3 Results in dynamic output

They are obtained in a purely analog form: output voltage of the computer amplifiers developing between + and - 100 V with an operational frequency range limited to 100 cycles.

## 2.2 Arithmetical computers

The customary input and output supports are:

- 1. Perforated tapes (1620),

- 2. Punched cards (7090 and 1620 with extension), and

- 3. Printer or typewriter.

### 2.2.1 Static linkage

The use of punched cards for intermediate phases where the information support makes manual transport possible will be generalized.

To eliminate this support, the definitive stage will necessitate the creation of direct transcoding apparatus, using electric signals before card punching, but the communication path will be at the level of the punch and reader.

| yped by             | Corrections | proofrend | by |

|---------------------|-------------|-----------|----|

| 1.                  | Corrections |           | -  |

| creections typed by | Final check | . by      |    |

## 2.2.2 Dynamic linkage

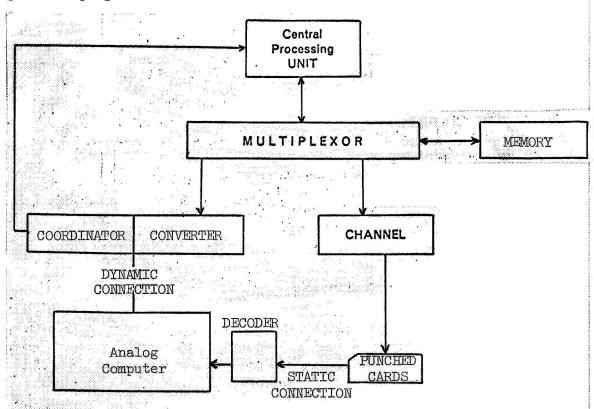

The solutions heretofore adopted of which we are cognizant all had the disadvantage of blocking the digital item for the benefit of the analog item, in consequence of the direct access of the transcoders to the memory. To avoid this immobilization, communication ought to be effected at the channel level, but with the possibility of calling from the analog side. It will thus be necessary to design a special channel system comprising a certain number of registers associated with analog-digital and digital-analog transcoders, and an operations coordinator (Figure 1).

By this means, communication with the memory will not immobilize the entire 7090 computer assembly but will enter into the sequence of programs in progress.

Figure 1. Junction between Analog Installation and IBM 7090

# 3. Definition of Contemplated Technical Stages

In order to retain a constant check on the scope of obtained results and a clear view of the volume of research and of budgetary requirements

| Typed by             | Corrections | proofe | ගේ | by      |

|----------------------|-------------|--------|----|---------|

| Proofreed by         | Corrections | cut in | by |         |

| Corrections typed by | Final check | by     |    | - 1-1-1 |

involved by the development of the linkage, it is preferable to establish a succession of well defined stages.

As has been seen, two linkage types are presented, bound to the computer concept:

- 1. A one-way digital-analog linkage permitting automatic setup of the problem, which could be described as an "analog structure linkage,"

- 2. A two-directional linkage in which analog variables can be treated by the digital computer, which after processing of these data can:

- a. Either act via the structural linkage, or

- b. Reintroduce new variables at the level of the analog items.

Up to a certain point these problems are independent. In fact, with the restriction of abandoning the structural linkage in the second possible arrangement, and of not contemplating digital participation except as a sophisticated organ of analog computation, the latter could be developed before the former.

We will however keep the order in this discussion that corresponds to the growing closeness of the linkage, even if its order must be modified in the course of actual embodiment.

- 3.1 Linkages in the digital-to-analog direction

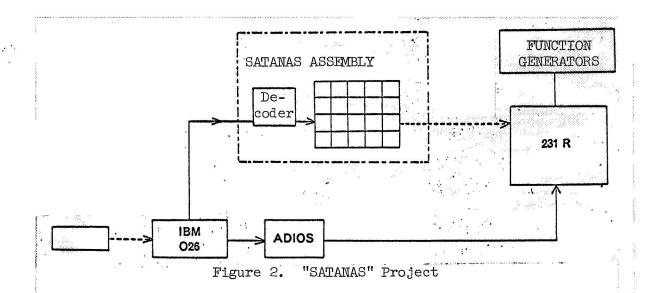

- 3.1.1 SATANAS project (Semi AuTomatic ANalog Setting)

A first rapidly accessible embodiment is the exploitation of information of address of elements furnished by APACHE 2, reducing the setup of patchboards to a purely manual operation.

A panel with luminous points will be controlled by a relay decoder starting from punched cards furnished by the program and indicating the start and the completion of each connection to be established. A patent application for this will be filed immediately. The inexpensive assembling has the advantage of development within a reasonable time. Though the automation thus obtained is only a semi-automation in which manipulation still occurs at the levels of: Transfer of punched cards, and Setup of the patchboard and its installation on the machine; it does already permit testing of the operation of the "address" part of APACHE 2, and the acquisition of experience for the succeeding phase. In this stage, the addressing consists simply in the assignment of analog items according to availability, after preliminary selection of types of nonlinearities upon reduction of the program. A limited number of simple rules will permit rational organization of a panel.

| Cyped by             | Corrections | proofree  | d by |

|----------------------|-------------|-----------|------|

| Proofreed by         | Corrections | cut in by |      |

| Corrections typed by | Final check | bу        |      |

The reliability of setup will be very much enhanced and an important time saving will result from elimination of errors in this phase of the work.

On the other hand, the transcoder for perforated cards to tapes to translate the digital information coming from the APACHE 2 processing has already been effected in the form of an internal modification of the ADIOS console (Ref. 10) and of an IBM 026 card punch used in reading.

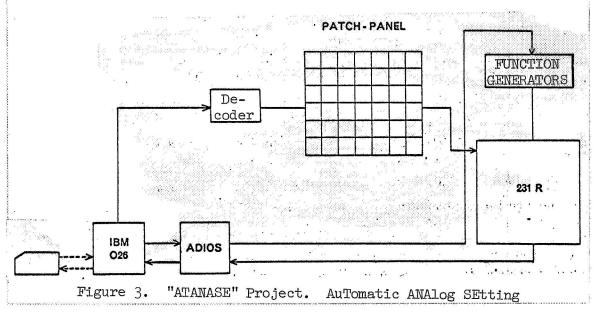

## 3.1.2 ATANASE project (Automatic ANAlog Setting)

This stage develops naturally in principle from the preceding one. This time without external intervention, it is a question of effecting complete setup of a problem with command originating in exploitation of a digital program. Figure 2 shows clearly the points at which it is suitable to introduce an automatic arrangement: patchboard and function generators.

For these latter a version designed by Electronic Associates should allow direct setup of the potentiometer slopes controlled by the more expensive ADIOS system (D.D.F.G.) and occupying more space than present function generators. They have the advantage of being substantially automatic. In fact the present verification by static check only takes into account one point on the curve and manual setup requires a rigorous check independent of the static check.

The problem of the automatic patchboard is technically much more difficult: a board represents a possibility of connections between outputs and inputs of items whose number, taken without any restriction, approximates 3,000,000.

Taken in this form, a commutation system is practically impossible to achieve: but a more systematic study of the organization of a board makes apparent: exclusions, preferred structures, a breakdown of the block diagrams into subunits connected by a small number of variables corresponding in general either to a physical localization due to the structure proper of the unit to be designed, or to a localization due to the mathematical processing (passage to finite differences in a partial differential equation system).

In advancing this idea and taking into account a certain number of restrictions stemming from statistical studies, there should emerge an automatic distributor of about 10,000 contacts, according to preliminary estimates. There is a return to possible orders of magnitude; the use of relays or of a step-by-step arrangement is imposed by the quality of the connections that is to assume the integral character of the transmission of analog voltages.

| Typed by             | Corrections | proofreed | by                                      |

|----------------------|-------------|-----------|-----------------------------------------|

| Proofreed by         | Corrections | cet in by | *************************************** |

| Corrections typed by | Final check | . by      |                                         |

7

In parallel, the organization of the address code will be completed to take into account restrictions, exclusions and a relative optimization of the application of the computer elements. The first stage of this study will consist in simulating on the IBM 7090 the various possible arrangements of automatic patchboards and comparing their efficiency and simplicity of principle. A basic redesign of the present computer structure required by the exigencies of technology is not ruled out.

At the conclusion of this study a setup system will be available that is completely freed from the manual intervention of the operator. Only the transfer of punched cards will be necessary (Figure 3).

| Typed by             | Corrections | proofreed | by |

|----------------------|-------------|-----------|----|

| Proofreed by         | Corrections | cut in by |    |

| Corrections typed by | Final check | . Бу      |    |

But it is well to stress the technical difficulties presenting a multiplicity of problems in the development of the setup panel: contact quality, command systems, quantity of materiel, organization of the address system, possible parallel manual intervention, method of control.

- 3.2 Two-way linkage

- 3.2.1 CRESSIDA project (Couplage REverSible StatIque Digital Analog) (Two-way static digital-analog linkage)

In the two preceding projects the transfer of information from the digital computer to the analog input elements is effected by means of two successive supports, punched cards, perforated tape.

Another possibility ought to be the elimination of this double translation which can be considered as practically independent. Indeed, a minimal modification of the ADIOS system makes it possible for word-forword acceptance of coded information. This information can be furnished directly without the perforated tape phase, starting from a perforator assembly adjacent to the reader; the furnished electric signals would be substituted for the signals furnished by the ADIOS reader. Similarly, output data from ADIOS would be taken ahead of its perforator system and referred to the card punch. Human intervention would be confined to the carrying of cards between 1401 and the perforator.

Finally a detailed study of the electric signals should make it possible to develop an adapter to assure direct static connection with channel 7090 as indicated in Figure 1.

3.2.2 CANDIDE project (Couplage ANalog DIgital DynamiquE) (Dynamic analog-digital linkage)

The problem is to cause all or part of the analog values simultaneously in play to be communicated to the digital computer either as a discrete sample or continuously. Several types of high speed converters already exist, for example, ADDALINK converters built by Electronic Associates and ADDAVERTER (EPSCO), etc. Thus there could be used:

- 1. Either a number of converters equal to the analog channels to be translated to digital and vice versa (continuous linkage), or

- 2. Multichannel electronic commutation devices each followed by a single converter (sampling linkage).

A problem of operations synchronization is added to the problem of apparatus:

1. Clearing the memories of the 7090,

| Typed by             | Corrections | proofreed | Ъу |

|----------------------|-------------|-----------|----|

| Proofreed by         | Corrections | cut in by |    |

| Corrections typed by | Finel check | ъу        |    |

- 2. Setting into operation the program that answers the digital part of the analog problem, and

- 3. Orders for initiation and ending computation transferred to the 7090.

All the above constitutes only a bare outline of the problem (speed, synchronization, compatibility of signals, study of specific programs, etc.) which should be examined in detail.

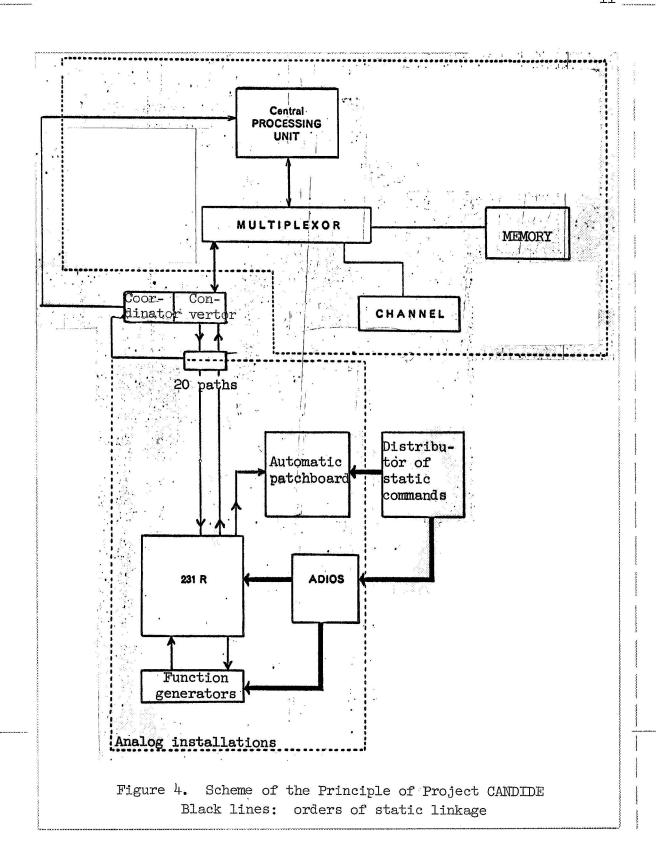

In fact this dynamic linkage has already been used in special cases (Ref. 5) but not with possible digital processing of the results and reactions on the block diagram structure. The definitive stage would consist in putting simultaneously into play this dynamic linkage using the digital computer as a "super-generator of functions" with extensive possibilities during the computer phase and hence a dependence upon the analog installation, and as a "structure corrector" taking into account a congeries of results to prepare a new setup in the static phase, under the direct control of the digital installation.

The synoptic schema of the installation would then be as appears in Figure 4.

## 4. Ancillary Studies

A whole series of problems could be attacked in parallel with the technical studies of linkage. Among others they relate to:

- 1. Automatic verification of functioning of the analog materiel,

- 2. Constitution of a library of subroutines in APACHE 2,

- 3. Special programs related to problems to be solved,

- 4. A mathematical analysis of the new tool thus constituted in its two aspects, structural linkage, dynamic linkage, and their application, and

- 5. Special application of the linkage of project CARN.

# 4.1 Automatic verification of analog function

#### 4.1.1 Automatic maintenance

To save time in the effective utilization of analog machines, it is possible to bring up the problem of automatic maintenance. This could be accomplished by:

- l. A scheme for putting the whole of the material into play by means of a setup panel with special fixed wiring,

- 2. An ADIOS tape setting up all the potentiometers from a special APACHE program and fixing the necessary computing operations,

Aprila Mode groefred by ...... The Posts April by .... The Exhant by

Consections or solvest by \_\_\_\_\_\_\_

Torus are out in by \_\_\_\_\_\_

that check by

3. Special elements as noise detector, and

4. A series of static tests processed digitally (project CRESSIDA) and furnishing the list of defective units.

This embodiment can extend to various kinds of multipliers: a special method could be developed for function generators with manual setup.

## 4.1.2 Static check processing

In principle all the information bits of the static check can be processed digitally. A comparison of obtained actual values and desired values for different derivatives could be done automatically.

In any case this operation would be of interest only insofar as a method could be developed that would provide a means for determining the exact points of sources of error.

## 4.2 Constitution of a library of subroutines in APACHE 2

The block diagrams corresponding to classic problems often reproduced: kinetics of nuclear reactors, perturbation functions in mathematical form (Bessel function, attenuated or divergent sinusoids, exponential superpositions, etc.), transfer functions in general, could be the subject matter of library programs. Similarly a mathematical processing of data such that the breakup of finite differences of equations to partial derivatives in classic form could enter into this framework.

## 4.3 Special programs connected with problems to be solved

The present subject is too enormous to be attacked within the limits of this report. A preliminary study of each problem will be necessary to acquire the desired experience. A special application of great importance could be the operation of the floating decimal analog computer, i.e., a preliminary setup taking into account maximal known values of variables would automatically be corrected by the digital computer after the initial calculation phase within a limited period to reset the variables with unknown limits. On the other hand a lower limit being established for the principal variables, any passing beyond this limit would give rise to a new setting of the limits.

## 4.4 Mathematical analysis of the new tool

A new discipline related to the hybrid installation should be developed. It should integrate the principal problems not yet resolved by

| Typed by             |  |

|----------------------|--|

| Proofrend by         |  |

| Corrections typed by |  |

classic methods: generation of variable delays, optimization of coefficients of differential equations from a known response, synthesis of transfer functions taking into account the pulsed response of a system (Refs. 13, 14).

## 4.5 Application to the CARN project

The most important application of the linkage technique is clearly a contribution to Calcul Automatique de Reacteurs Nucleaires (Automatic Computation of Nuclear Reactors) towards which development all the partial studies already described ought to be directed: optimization of coefficients, equation system synthesis, variable delays, processing of partial derivative equations. A possible study of additive linkage of a resistor network (Ref. 12) to the hybrid installation already described ought to afford greater potentialities for this (simulation of reactors in theory to two groups, heterogeneity of media, etc.).

Certain new techniques concerning active networks using a time quantification according to a principle derived from digital methods (Ref. 11) could acquire flexibility and speed by linkage with a digital computer. It is indeed possible to attack parabolic and hyperbolic equations with these techniques with an assured loop stability from one stage to the other.

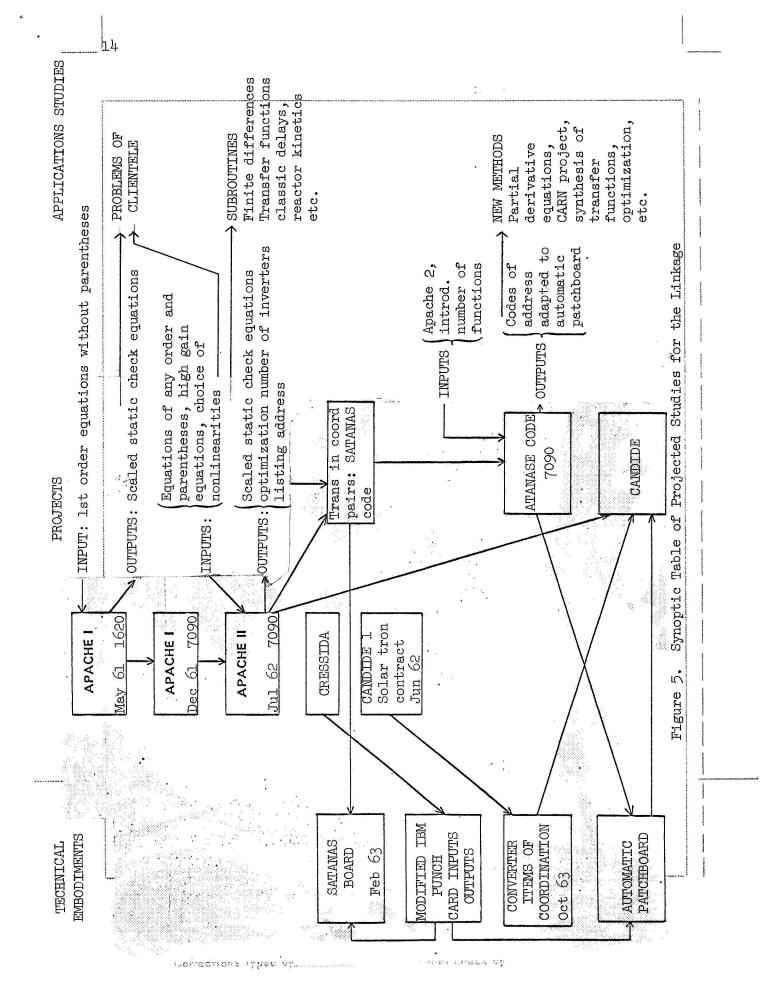

#### 5. Conclusions

A single line of attack emerges immediately from the congeries of problems posed by the linkage of the two types of computers. In fact, the distinction between structural linkage and dynamic linkage permits a parallel development: the SATANAS project being immediately obtainable, while projects CRESSIDA and CANDIDE 1 can be advanced independently of project ATANASE concerning which fundamental questions of construction still exist.

In any case, the conjunction of CRESSIDA and CANDIDE 1 will already offer extensive possibilities in the realm of automatic advance projects, and the study of its application to CARN will indicate a line of procedure in reference to special efforts to be carried out for the definitive realization of CANDIDE 2.

Finally, the analysis of methods using passive and active impedance networks and investigation of their possible linkage with the two types of computers envisioned in this report will be able to provide a still greater development of the tools of a great Computer Center. It is possible indeed to imagine a meshed network representing a heterogeneous medium to which would be applied conditions at the limits and injections at

Procheod by Corrections typed by

Corrections prockned by

Corrections and to by

The hadday

the nodes ("second member" terms) which would be variable as a function of time, furnished by an analog computer. The exploitation of the results (inventory of the field in special areas, interpolation being assured by the digital computer which could--on condition of the compatibility of computing time--furnish new data for the limiting conditions to the analog computer. A retroaction of the field on limiting conditions would then be feasible.

In any case, the conjunction of the two computer disciplines cannot but be fruitful through the changes of viewpoint that it requires of the respective specialists.

#### Bibliography

- 1. McLeod, J. H. and Leger, R. M. Combined Analog and Digital Systems, Wiley, When and How, Instruments and Automation, Vol. 30, No. 6, June 1957.

- 2. Maxwell, Paul The General Trend Towards Digital Analogue Techniques. Actes des 2nd Journées Internationales de Calcul Analogique, Strasbourg, 1958.

- 3. Braffort, P., Caillet, C. and Gamp, J. De la Compétition à la Collaboration entre les techniques analogique et digitale du Calcul Numérique (From Competition to Collaboration Between the Analog and Digital Techniques of Numerical Computation). I.C.I.P., UNESCO, Paris, 1959.

- 4. Ohlinger, L. ANATRAN First Step in Breeding the DIGINALOG. Proceedings of the Western Joint. Computer Conference, Vol. 17, May 3, 1960.

- 5. Shapiro, S., Lapidus, L., Harris, G. and Lee, C. Simulation of Chemical Processes on a Combined Analog-Digital Computer. Séminaire sur le Calcul Analogique appliqué aux Processus Chimiques, Bruxelles, 21-23 November 1960.

- 6. Archibald, J. T. Analog-Digital Computing Methods. Séminaire sur le Calcul Analogique appliqué aux Processus Chimiques. Bruxelles, 21-23 November 1960.

- 7. Del Bigio, G. P. and d'Hoop, H. Analog Programming and Checking (APACHE 1), Rapport EURATOM EUR 189.f, January 1963.

- 8. Witzel, T. and Wilson, J. L. Digital Computer-Programs Analog Solutions, Vol. 8, No. 6, June 1961.

- 9. Diebold, J. et al. The Hybrid Computer. Automatic Data-Processing, July 1961.

- 10. Van Wauwe, A. Modifications apportées à l'ADIOS en vue de l'utilisation du code APACHE 2 (Modifications of ADIOS for the Purpose of Utilization of APACHE 2 Code). Rapport EURATOM, in press.

- 11. Green, C., Debroux, A., Del Bigio, G. P. and d'Hoop, H. Le code

APACHE destiné à la programmation d'un problème analogique au moyen

| Typed by             | Corrections proofeed by |

|----------------------|-------------------------|

| Prochece by          | Consections cofficient  |

| Corrections typed by | Clark about by          |

d'un calculateur digital (The APACHE Code Intended for Programming of an Analog Problem by Means of a Digital Computer). Communication to the 3rd Journees Internationales de Calcul Analogique OPATIJA, September 1961.

Karplus, W. A New Active-Passive Network Simulator for Transient Field Problems. Proceedings of the I. R. E., Special Issue on Com-

puters, Vol. 46, No. 1, January 1961.

13. Girerd, J. and Riotte, A. L'analyseur Différentiel à réseau Delta 600 (The Differential Analyser, Delta 600 Network). L'Onde Electrique, December 1960.

14. Matyash, I. Methods of Analog Computer Solutions of Linear Differential. Equations with Variable Coefficients. Automation and Re-

mote Control, Vol. 20, No. 7, July 1959.

On the Properties of the Impulsive Response Function 15. Borskii, V. of Systems with Variable Parameters. Automation and Remote Control, Vol. 20, No. 7, July 1959.

16. Green, C. The EURATOM Computer Linkage System. Rapport EURATOM,

à paraître.

Franslated for the National Aeronautics and Space Administration by John F. Holman and Co. Inc.

| Typed by             | Corrections prontied by |  |

|----------------------|-------------------------|--|

| Proofreed by         | Caractara aut in by     |  |

| Corrections typed by | Theolohedk by           |  |